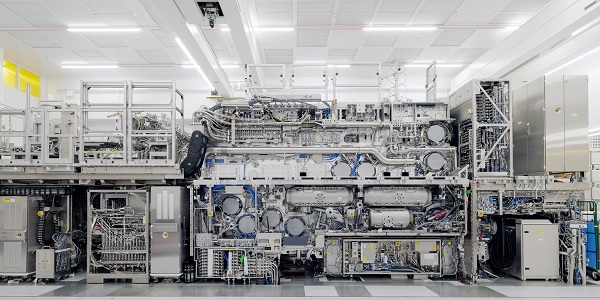

▲ TSMC가 차세대 노광 장비인 하이NA EUV 도입 시기를 예상보다 늦추며 인텔에 기술 추격 기회를 열어주고 있다는 평가가 나온다. ASML의 하이NA EUV 반도체 장비 사진.

TSMC보다 먼저 하이NA 장비 도입을 확정한 인텔이 기술 추격에 속도를 낼 기회가 열릴 것으로 전망된다.

29일 IT전문지 WCCF테크는 “TSMC가 A14(1.4나노급) 공정에 하이NA EUV를 생략하기로 했다”며 “인텔 파운드리가 TSMC에 기술적 우위를 확보할 수 있다”고 보도했다.

하이NA EUV는 네덜란드 ASML이 독점 공급하는 신형 극자외선(EUV) 반도체 노광장비를 활용하는 기술이다.

2나노 미만 미세공정 반도체의 생산 효율성과 성능을 높일 수 있어 차세대 핵심 기술로 주목받고 있다.

삼성전자와 TSMC, 인텔은 모두 차세대 파운드리 공정에 하이NA 기술 도입을 추진하고 있다. 다만 시기를 분명하게 확정지은 반도체 제조사는 인텔뿐이다.

인텔은 올해 양산을 앞둔 18A(1.8나노급) 공정부터 순차적으로 하이NA 장비를 활용해 반도체 기술 경쟁력 강화에 주력하겠다는 계획을 두고 있다.

TSMC는 이를 뒤따라 1.4나노급 공정부터 하이NA EUV를 도입할 것이라는 전망이 유력하게 나왔다.

그러나 TSMC는 최근 기술 심포지엄에서 해당 기술 적용을 1.4나노 이후 공정으로 미루겠다는 계획을 발표하며 시장의 예측을 벗어났다.

WCCF테크는 TSMC가 반도체 성능보다 경제성을 우선순위로 두고 이런 결정을 내렸다고 해석했다.

하이NA EUV 장비는 기존 제품과 비교해 비용 부담이 큰 데다 도입 초기에는 오히려 생산성이 낮아져 일시적으로 실적 악화를 이끌 가능성이 있기 때문이다.

TSMC는 1.4나노급 파생 공정인 A14P를 상용화할 때 하이NA EUV 적용을 검토한다는 방침을 두고 있다. 이는 2029년부터 양산이 계획된 파운드리 공정이다.

결국 TSMC가 하이NA EUV 장비를 본격적으로 활용하는 시기가 인텔보다 약 4년 늦어지는 셈이다.

만약 인텔이 하이NA 장비를 파운드리 1위 기업인 TSMC보다 일찍 도입한 성과를 온전히 거둔다면 수 년째 뒤처지던 기술력을 빠르게 추격할 기회를 얻을 수 있다.

반도체 파운드리 단가 측면에서도 인텔이 TSMC에 우위를 차지하며 고객사 위탁생산 수주 확보에 강력한 장점을 확보하게 될 가능성도 있다.

WCCF테크는 “TSMC의 하이NA 기술 도입 지연은 경쟁사들에 유리한 환경을 만들어주는 결정이 될 수 있다”고 바라봤다.

다만 TSMC가 하이NA EUV를 대체할 수 있는 자체 ‘멀티패터닝’ 기술을 상용화해 원가 절감에 성과를 내며 이를 충분히 만회할 수 있다는 전망도 제시됐다. 김용원 기자